# Neural architectures for database query processing, syntax analysis, knowledge representation, and inference

by

Chun-Hsien Chen

A dissertation submitted to the graduate faculty in partial fulfillment of the requirements for the degree of  ${\tt DOCTOR\ OF\ PHILOSOPHY}$

Major: Computer Science

Major Professor: Vasant Honavar

Iowa State University

Ames, Iowa

1998

Copyright © Chun-Hsien Chen, 1998. All rights reserved.

### Graduate College Iowa State University

## This is to certify that the Doctoral dissertation of Chun-Hsien Chen

has met the dissertation requirements of Iowa State University

| Committee Member         |

|--------------------------|

| Committee Member         |

| Committee Member         |

| Committee Member         |

| Major Professor          |

| For the Major Program    |

| For the Graduate College |

## TABLE OF CONTENTS

| A | ACKNOWLEDGEMENTS       |         |                                                                            |    |

|---|------------------------|---------|----------------------------------------------------------------------------|----|

| A | ABSTRACT               |         |                                                                            |    |

| 1 | IN                     | ГROD    | UCTION                                                                     | 1  |

|   | 1.1                    | Artific | ial Neural Networks                                                        | 3  |

|   |                        | 1.1.1   | Artificial neural units                                                    | 3  |

|   |                        | 1.1.2   | Activation functions                                                       | 4  |

|   |                        | 1.1.3   | Types of artificial neural networks and their computational capabilities   | 5  |

|   |                        | 1.1.4   | Implementation of artificial neural networks                               | 6  |

|   | 1.2                    | A Brie  | ef Review of Artificial Neural Networks                                    | 6  |

|   | 1.3                    | An Ov   | verview of the Dissertation                                                | 9  |

| 2 | <b>A</b> :             | NEUR    | AL MEMORY FOR CONTENT AS WELL AS ADDRESS-                                  |    |

|   | $\mathbf{B}\mathbf{A}$ | SED S   | STORAGE AND RECALL                                                         | 13 |

|   | 2.1                    | Introd  | uction                                                                     | 13 |

|   |                        | 2.1.1   | Information retrieval and binary mapping                                   | 14 |

|   |                        | 2.1.2   | Associative memory (Content-addressed memory)                              | 15 |

|   |                        | 2.1.3   | Address-based memory                                                       | 18 |

|   |                        | 2.1.4   | Perceptrons                                                                | 19 |

|   | 2.2                    | Multi-  | layer Perceptrons as Neural Memories                                       | 19 |

|   |                        | 2.2.1   | The application of linear separability of binary vertices in pattern clas- |    |

|   |                        |         | sification                                                                 | 20 |

|   |                        | 2.2.2   | Best match: pattern classification with precision control                  | 23 |

|   |                        | 2.2.3   | Storage capacity                                                           | 24 |

|   |     | 2.2.4                 | Synthesis of associative and address-based memories                         | 24 |

|---|-----|-----------------------|-----------------------------------------------------------------------------|----|

|   |     | 2.2.5                 | Exact match: binary mapping Perceptron (BMP) module                         | 27 |

|   |     | 2.2.6                 | Conversion between memory models using bipolar and binary inputs            | 28 |

|   | 2.3 | Prope                 | rties of the Proposed Neural Associative Memory                             | 32 |

|   |     | 2.3.1                 | Partial match: associative recall from a partially specified input          | 33 |

|   |     | 2.3.2                 | Multiple associative recalls                                                | 35 |

|   |     | 2.3.3                 | Fault tolerance                                                             | 38 |

|   | 2.4 | Summ                  | ary and Discussion                                                          | 40 |

| 3 | NE  | URAI                  | ARCHITECTURES FOR INFORMATION RETRIEVAL AND                                 |    |

|   | DA  | TABA                  | SE QUERY PROCESSING                                                         | 42 |

|   | 3.1 | Introd                | uction                                                                      | 42 |

|   |     | 3.1.1                 | Information retrieval in neural associative memories                        | 44 |

|   | 3.2 | Query                 | Processing Using Neural Associative Memories                                | 45 |

|   |     | 3.2.1                 | Realization of lexical access for a machine-readable lexicon using a neural |    |

|   |     |                       | associative memory                                                          | 45 |

|   |     | 3.2.2                 | Realization of a library query system using a neural associative memory     | 49 |

|   |     | 3.2.3                 | The implementation of case insensitive pattern matching                     | 52 |

|   | 3.3 | $\operatorname{Comp}$ | arison with Other Database Query Processing Techniques                      | 53 |

|   |     | 3.3.1                 | Performance of current electronic realization for neural networks           | 53 |

|   |     | 3.3.2                 | Analysis of query processing in conventional computer systems               | 54 |

|   | 3.4 | Summ                  | ary and Discussion                                                          | 58 |

| 4 | NE  | URAI                  | ARCHITECTURES FOR ELEMENTARY LOGICAL INFER-                                 |    |

|   | EN  | CE .                  |                                                                             | 59 |

|   | 4.1 | Introd                | uction                                                                      | 59 |

|   | 4.2 | Neura                 | l Assemblies for the Recognition of Partial Patterns                        | 60 |

|   |     | 4.2.1                 | A neural assembly for inclusive recognition                                 | 61 |

|   |     | 4.2.2                 | A neural assembly for exclusive recognition                                 | 62 |

|   | 4.3 | A Neu                 | ral Assembly for Executing a Logical AND (AND Neural Assembly)              | 64 |

|   | 4.4 | Neural                     | Assemblies for Executing Logic ORs (OR Neural Assemblies)                     | 67  |

|---|-----|----------------------------|-------------------------------------------------------------------------------|-----|

|   |     | 4.4.1                      | A general OR neural assembly                                                  | 67  |

|   |     | 4.4.2                      | A monotone OR neural assembly                                                 | 69  |

|   | 4.5 | A Neur                     | ral Architecture for Realizing DNF Boolean Functions                          | 70  |

|   | 4.6 | Summa                      | ary and Discussion                                                            | 71  |

| 5 | NE  | URAL                       | ARCHITECTURES FOR SEQUENCE PROCESSING                                         | 73  |

|   | 5.1 | Introdu                    | action                                                                        | 73  |

|   |     | 5.1.1                      | Symbolic functions and binary mappings                                        | 74  |

|   | 5.2 | Neural                     | Network Design for Deterministic Finite Automata (NN DFA) $\ \ldots \ \ldots$ | 76  |

|   |     | 5.2.1                      | Deterministic finite automata (DFA)                                           | 76  |

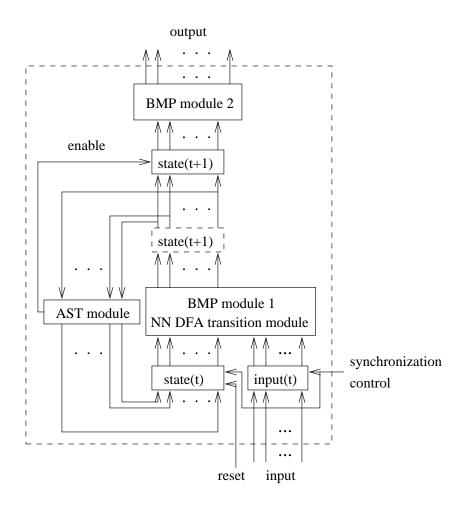

|   |     | 5.2.2                      | Architecture of NN DFA                                                        | 77  |

|   | 5.3 | Neural                     | Network Design for Deterministic Pushdown Automata (NN DPDA)                  | 80  |

|   |     | 5.3.1                      | $Deterministic\ pushdown\ automata\ (DPDA)\ \dots\ \dots\ \dots$              | 80  |

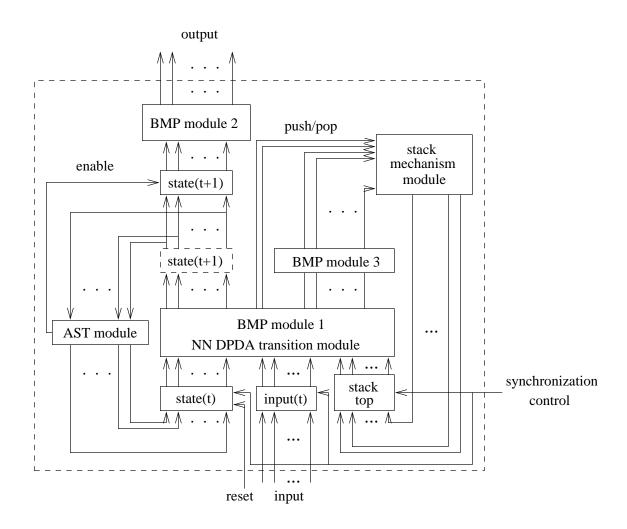

|   |     | 5.3.2                      | Architecture of NN DPDA                                                       | 81  |

|   | 5.4 | Neural                     | Network Design for Stack (NN Stack)                                           | 84  |

|   |     | 5.4.1                      | Symbolic representation of stack                                              | 84  |

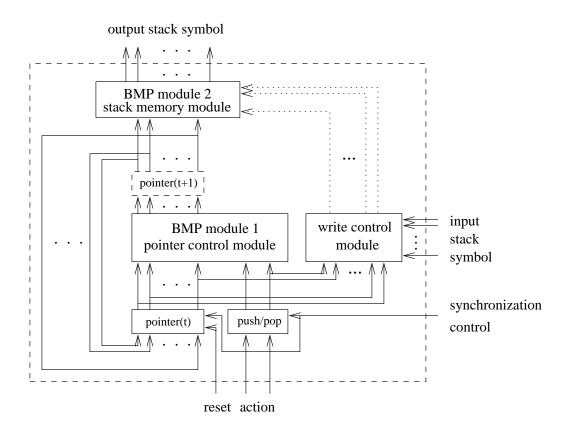

|   |     | 5.4.2                      | Architecture of NN Stack                                                      | 85  |

|   |     | 5.4.3                      | NN Stack in action                                                            | 89  |

|   | 5.5 | Neural                     | Network Design for Nondeterministic Finite Automata (NN NFA) $\ . \ . \ .$    | 90  |

|   |     | 5.5.1                      | Nondeterministic finite automata (NFA)                                        | 91  |

|   |     | 5.5.2                      | Model for concurrently tracking all the possible nondeterministic moves       |     |

|   |     |                            | in the operation of an NFA using RNN                                          | 92  |

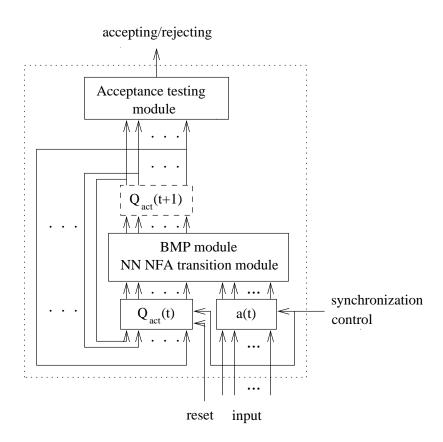

|   |     | 5.5.3                      | Architecture of NN NFA                                                        | 95  |

|   |     | 5.5.4                      | Proof of correctness                                                          | 103 |

|   |     | 5.5.5                      | NN NFA in Action                                                              | 105 |

|   | 5.6 | Summa                      | ary and Discussion                                                            | 106 |

| 6 | NE  | $\overline{\mathbf{URAL}}$ | ARCHITECTURES FOR SYNTAX ANALYSIS                                             | 107 |

|   | 6.1 | Introd                     | uction                                                                        | 107 |

|   | DII | OGR A  |                                                                                 | 137 |

|---|-----|--------|---------------------------------------------------------------------------------|-----|

| 7 | CO  | NCLU   | SION                                                                            | 136 |

|   | 6.5 | Summ   | ary and Discussion                                                              | 132 |

|   |     | 6.4.2  | Performance analysis of LR parser                                               | 130 |

|   |     | 6.4.1  | Performance analysis of lexical analyzer                                        | 128 |

|   | 6.4 | Perfor | mance Analysis                                                                  | 127 |

|   |     | 6.3.4  | NNLR Parser in action                                                           | 122 |

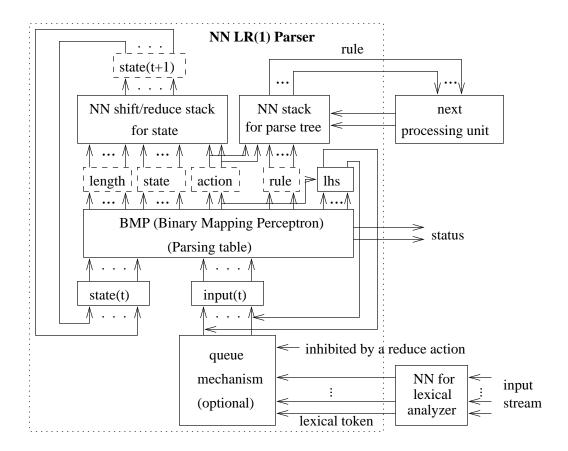

|   |     | 6.3.3  | Architecture of NNLR parser                                                     | 120 |

|   |     | 6.3.2  | Representation of parsing moves and parse trees                                 | 119 |

|   |     | 6.3.1  | Representation of parse table                                                   | 115 |

|   | 6.3 | A Mod  | lular Neural Architecture for LR Parser (NNLR Parser)                           | 115 |

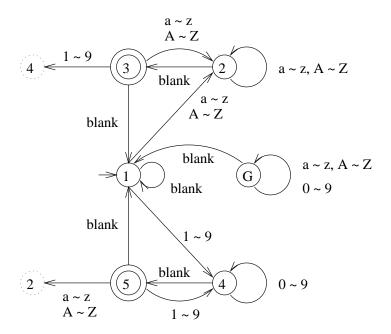

|   |     | 6.2.2  | Neural network design for a word lookup table (NNLTab) $\ \ldots \ \ldots$      | 114 |

|   |     | 6.2.1  | Neural network design for a word segmenter (NNSeg) $\ \ldots \ \ldots \ \ldots$ | 112 |

|   | 6.2 | Neural | Network Design for a Lexical Analyzer (NNLexAn)                                 | 111 |

|   |     | 6.1.1  | Review of related research on neural architectures for syntax analysis .        | 108 |

## LIST OF FIGURES

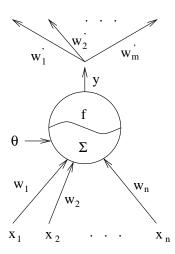

| Figure 1.1 | A typical computing unit of an ANN                                                    | 4  |

|------------|---------------------------------------------------------------------------------------|----|

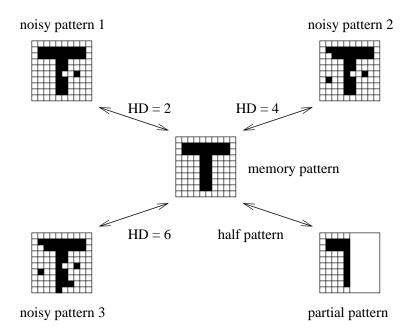

| Figure 2.1 | Examples of memory pattern, noisy patterns, and partial pattern                       | 17 |

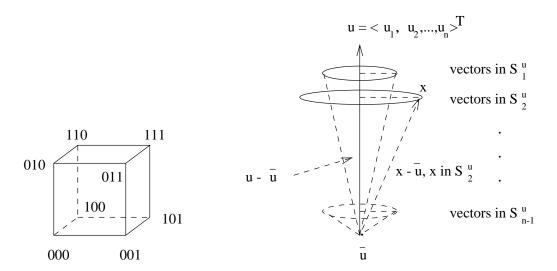

| Figure 2.2 | The spatial distribution of a 3-dimensional and an $n$ -dimensional binary            |    |

|            | hypercubes                                                                            | 22 |

| Figure 2.3 | The setting of connection weights and hidden node threshold in the                    |    |

|            | proposed neural memory (a 2-layer Perceptron with binary input) for                   |    |

|            | a given associated memory pair                                                        | 26 |

| Figure 2.4 | The settings of connection weights and hidden node threshold in the                   |    |

|            | proposed BMP module for an associated binary mapping ordered pair                     | 28 |

| Figure 2.5 | The setting of connection weights and hidden node threshold in the                    |    |

|            | proposed neural memory (a 2-layer Perceptron with bipolar input) for                  |    |

|            | a given associated memory pair.                                                       | 32 |

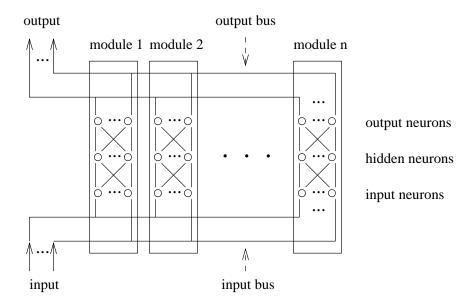

| Figure 3.1 | A modular design of the proposed ANN memory for easy expansion.                       |    |

|            | This 1-dimensional array structure can be easily extended to 2 or 3-                  |    |

|            | dimensional array structures.                                                         | 50 |

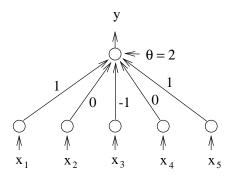

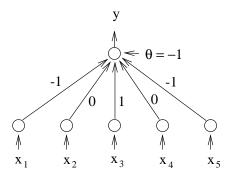

| Figure 4.1 | A 1-layer Perceptron which recognizes all the 5-dimensional binary pat-               |    |

|            | terns that contain the partial pattern $<1,?,0,?,1>$ , where ? denotes                |    |

|            | don't care                                                                            | 63 |

| Figure 4.2 | A 1-layer Perceptron which recognizes all the 5-dimensional binary pat-               |    |

|            | terns that don't contain the partial pattern $\langle 1,?,0,?,1\rangle$ , where ? de- |    |

|            | notes don't care                                                                      | 65 |

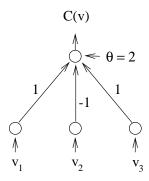

| Figure 4.3 | An AND neural assembly which realizes the logical AND function $C(v)$ .             | 66  |

|------------|-------------------------------------------------------------------------------------|-----|

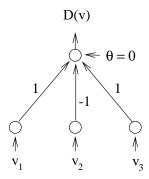

| Figure 4.4 | An ${\tt OR}$ neural assembly which realizes the logical ${\tt OR}$ function $D(v)$ | 69  |

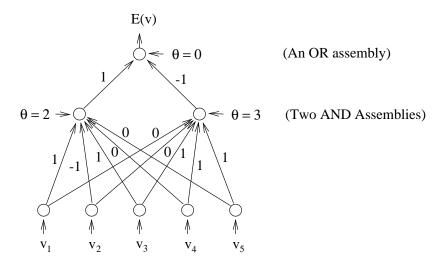

| Figure 4.5 | An neural architecture which realizes the DNF Boolean function $E(v)$ .             | 72  |

| Figure 5.1 | The proposed modular neural network architecture for DFA $$                         | 79  |

| Figure 5.2 | The proposed modular neural network architecture for DPDA $\ \ldots \ \ldots$       | 83  |

| Figure 5.3 | The proposed neural network architecture for stack mechanism                        | 86  |

| Figure 5.4 | The state diagram of an NFA that accepts any input string containing                |     |

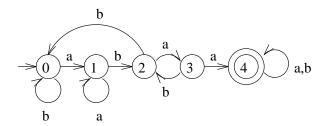

|            | the sub-string abaa                                                                 | 93  |

| Figure 5.5 | The state diagram of a DFA that accepts any input string containing                 |     |

|            | the sub-string abaa                                                                 | 93  |

| Figure 5.6 | The proposed recurrent neural network architecture for concurrently                 |     |

|            | tracking all the nondeterministic computations of a given NFA                       | 96  |

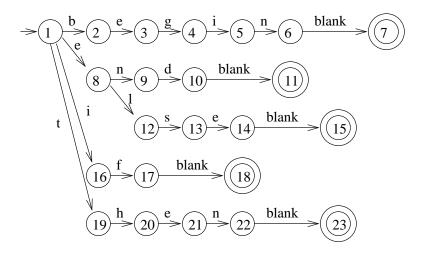

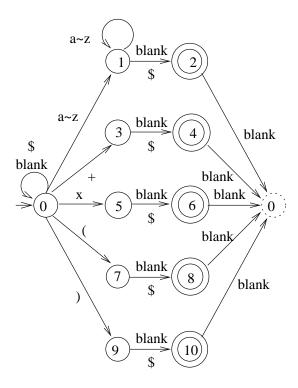

| Figure 6.1 | The simplified state diagram of a DFA which recognizes keywords :                   |     |

|            | begin, end, if, then, and else                                                      | 112 |

| Figure 6.2 | The state diagram of a DFA which simulates a simple word segmenter                  |     |

|            | carving continuous input stream of characters into words including in-              |     |

|            | teger constants, keywords and identifiers                                           | 113 |

| Figure 6.3 | The proposed neural network architecture for $LR(1)$ parser                         | 118 |

| Figure 6.4 | The state diagram of the DFA $M_{L_1}$ for the lexical analyzer $L_1$               | 126 |

## LIST OF TABLES

| Table 2.1 | The corresponding maximal storage capacity of a 1-layer Perceptron    |     |

|-----------|-----------------------------------------------------------------------|-----|

|           | with 100 input neurons for classifying binary patterns for a range of |     |

|           | allowable noise levels                                                | 25  |

| Table 3.1 | A comparison of the estimated performance of the proposed neural as-  |     |

|           | sociative memory with that of other techniques commonly used in con-  |     |

|           | ventional computer systems for locating a record pointer in key-based |     |

|           | organizations                                                         | 56  |

| Table 3.2 | A comparison of the capabilities of the proposed neural associative   |     |

|           | memory with those of other techniques commonly used in conventional   |     |

|           | computer systems for exact match and partial match                    | 56  |

| Table 6.1 | The parse table of the LR(1) parser for grammar $G_1$                 | 124 |

| Table 6.2 | The transition function $\delta_{L_1}$ of the DFA $M_{L_1}$           | 126 |

| Table 6.3 | Moves of the LR(1) parser for grammar $G_1$ on input string I×I+I     | 127 |

| Table 6.4 | A comparison of the estimated performance of the proposed NNLR        |     |

|           | Parser with that of conventional computer systems for syntax analysis | 132 |

#### ACKNOWLEDGEMENTS

I would like to express my sincere appreciation to Dr. Vasant Honavar for his support, assistance, and guidance, as well as challenging and inspiring criticism in the preparation of this dissertation and in my studies at Iowa State University. I would also like to thank my Graduate Committee: Dr. Tom Barta, Dr. Julie Dickerson, Dr. Les Miller, and Dr. Johnny Wong for their helpful advice, comments, and suggestions.

I am deeply indebted to the Extended and Continuing Education Office, Iowa State University, for the warm friendship of the staff, the valuable work experience, and the timely financial support without which my study for a Ph.D. would not be possible. I am grateful to Russell Meier and the Artificial Intelligence Research Group: Karthik Balakrishnan, Armin Mikler, Rajesh Parekh and Jihoon Yang for their friendship and inspiring discussion. I am also grateful to my friends in Ames, Iowa, for keeping me company at my leisure time and for nourishing me with friendship.

Also, I would like to express my deepest gratitude to my parents for their everlasting support and love.

#### ABSTRACT

Artificial neural networks, due to their inherent parallelism, potential for fault tolerance, and adaptation through learning, offer an attractive computational paradigm for a variety of applications in computer science and engineering, artificial intelligence, robotics, and cognitive modeling. Despite the success in the application of ANN to a broad range of numeric tasks in pattern classification, control, function approximation, and system identification, the integration of ANN and symbolic computing is only beginning to be explored. This dissertation explores to integrate ANN and some essential symbolic computations for content-based associative symbolic processing. This offers an opportunity to explore the potential benefits of ANN's inherent parallelism in the design of high performance computing systems for real time content-based symbolic processing applications. We develop methods to systematically design massively parallel architectures for pattern-directed symbol processing using neural associative memories as key components. In particular, we propose neural architectures for content-based as well as address-based data storage and recall, information retrieval and database query processing, elementary logical inference, sequence processing, and syntax analysis. Their potential advantages over conventional serial computer implementations of the same functions are examined in the dissertation.

#### 1 INTRODUCTION

The goal of artificial intelligence (AI), broadly interpreted, is to understand and engineer intelligent systems. It is often suggested that traditionally serial symbol processing systems of AI and inherently massively parallel artificial neural networks (ANN) offer two radically, perhaps even irreconcilably different paradigms for modelling minds and brains — both artificial as well as natural [130, 160]. AI has been successful in applications such as theorem proving, knowledge-based expert systems, mathematical reasoning, syntax analysis, and related applications which mainly involve systematic symbol manipulation. On the other hand, ANN have been particularly successful in applications such as pattern recognition, function approximation, and nonlinear control [60, 150] which involve primarily numeric computation. Meverowitz has suggested that the design of neural architectures capable of supporting dynamic representations for symbol manipulation is one of the grand challenges of neural network research [113]. As shown by Church, Kleene, McCulloch, Post, Turing, and others through their work on the theory of Computation [117, 100], both AI and ANN represent particular realizations of a universal (Turing-equivalent) model of computation [185]. Thus, despite assertions by some to the contrary, any task that can be realized by one can, in principle, be accomplished by the other. However, most AI systems have been traditionally programmed in languages that were influenced by Von Neumann's design of a serial stored program computer. ANN systems on the other hand, have been inspired by (albeit overly simplified) models of biological neural networks. They represent different commitments regarding the architecture and the primitive building blocks used to implement the necessary computations. Thus they occupy different regions characterized by possibly different cost-performance tradeoffs in a much larger space of potentially interesting designs for intelligent systems. Recently, several researchers have begun

to explore previously unexplored parts of this design space.

Given the reliance of both traditional AI and ANN on essentially equivalent formal models of computation, a central issue in design and analysis of intelligent systems has to do with the identification and implementation, under a variety of design, cost, and performance constraints, of a suitable subset of Turing-computable functions that adequately model the desired behaviors. Today's AI and ANN systems each demonstrate at least one way of performing a certain task (e.g., logical inference, pattern recognition, syntax analysis) naturally and thus pose the interesting problem for the other of doing the same task, perhaps more elegantly, efficiently, robustly, or cost-effectively than the other. In this context, it is beneficial to critically examine the often implicit and unstated assumptions on which current AI and ANN systems are based and to identify alternative (and potentially better) approaches to designing such systems. Massively parallel symbol processing architectures for AI systems or highly structured (as opposed to homogeneous, fully connected) ANN are just two examples of a wide range of approaches to designing intelligent systems [185, 72, 73]. Of particular interest are alternative designs (including synergistic hybrids of ANN and AI designs) for intelligent systems [47, 65, 70, 72, 73, 99, 136, 172, 179, 185]. Examples of such systems include: neural architectures for information retrieval and database query processing [23, 24], generation of context-free languages [187], rule-based inference [5, 31, 141, 167, 176], computer vision [11, 119], natural language processing [14, 32], learning [46, 69, 168], and knowledge-based systems [94, 145]. We strongly believe that a judicious and systematic exploration of the design space of such systems is essential for understanding the nature of key cost-performance tradeoffs in the synthesis of intelligent systems.

This dissertation explores to integrate ANN and some essential symbolic computations for content-based associative symbolic processing. This offers an opportunity to explore the potential benefits of ANN's inherent parallelism in the design of high performance computing systems for real time content-based symbolic processing applications.

#### 1.1 Artificial Neural Networks

ANN are biologically inspired by the neural systems of human brain which are massively parallel interconnected networks of hierarchically organized nerve cells (neurons). ANN are extremely simplified models of biological neural systems in many aspects such as the structure of basic computational units, the mechanism for information processing, network architecture, etc. Compared to most current digital computer systems, ANN are particularly well-suited for pattern-directed problems – pattern completion, pattern classification and pattern association [29] which arise frequently in applications such as language processing, speech recognition, and pattern recognition.

It is worth mentioning that the primary goal of ANN research (unlike neural modelling or computational neuroscience research) is not to discover a computational model for the detailed processes of human brain but to technologically pursue a computing paradigm which can effectively realize and efficiently perform high-level intelligent processes.

#### 1.1.1 Artificial neural units

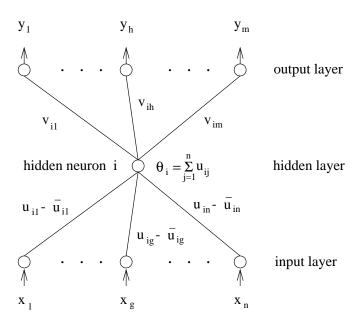

A typical computing unit (node) in an ANN has n input and m output connections, each of which has an associated weight. The node computes the weighted sum on the inputs, compares the sum to its node threshold, and produces its output based on an activation function. A commonly used activation function is threshold function. The resulting output is sent along the output connections to other nodes. The output of such a node used in this dissertation is defined by

$$y = f(s) \text{ and } s = \sum_{i=1}^{n} w_i x_i - \theta$$

(1.1)

where  $x_i$  is the value of input i,  $w_i$  is the associated weight on input connection i,  $\theta$  is the node threshold, y is the output value, and f is the activation function. Figure 1.1 shows such a node.

Figure 1.1 A typical computing unit of an ANN

#### 1.1.2 Activation functions

The types of activation functions used by an ANN affect its expressiveness, computational capabilities, and performance. Several typical activation functions are linear, binary sigmoidal, bipolar sigmoidal, binary hardlimiter, bipolar hardlimiter, gaussian, and ramp [56, 102] defined as follows:

linear:

$$f_L(s) = cs$$

, where  $s = \sum_{i=1}^n w_i x_i - \theta$  and  $c > 0$

binary sigmoidal:

$$f_S(s) = \frac{1}{1+e^{-cs}}$$

, where  $s = \sum_{i=1}^n w_i x_i - \theta$  and  $c > 0$

bipolar sigmoidal :

$$\check{f}_S(s) = \frac{1 - e^{-cs}}{1 + e^{-cs}}$$

, where  $s = \sum_{i=1}^n w_i x_i - \theta$  and  $c > 0$

binary hardlimiter:

$$f_H(s) = \begin{cases} 1 & \text{if } s \geq 0 \\ 0 & \text{otherwise} \end{cases}$$

, where  $s = \sum_{i=1}^n w_i x_i - \theta$

bipolar hard

limiter :

$$\check{f}_H(s) = \begin{cases} +1 & \text{if } s \geq 0 \\ -1 & \text{otherwise} \end{cases}$$

, where  $s = \sum_{i=1}^n w_i x_i - \theta$

gaussian :

$$f_G(s) = e^{\frac{-s}{2\sigma^2}}$$

, where  $s = \sum_{i=0}^n (w_i - x_i)^2$

ramp:

$$f_R(s) = \begin{cases} +1 & \text{if cs} > +1 \\ cs & \text{if } |\text{cs}| \le 1 \\ -1 & \text{if cs} < -1 \end{cases}$$

, where  $s = \sum_{i=1}^n w_i x_i - \theta$  and  $c > 0$

In above equations, c is activation gain. Note that most of the activation functions produce output in the range of [0,1] for binary signals, and [-1,1] for bipolar signals.

This dissertation uses two types of threshold functions: binary hardlimiter and bipolar hardlimiter. Their simplicity allows simple and efficient hardware implementation of such threshold functions.

#### 1.1.3 Types of artificial neural networks and their computational capabilities

ANN can be mainly classified into three basic categories: feedforward networks, feedback networks and recurrent networks [28, 56, 131] according to their architectures, functionalities, and signal propagation direction of their connections. The output of a feedforward network is a function of current input, and its connections are unidirectional. The output of a feedback network is a function of current input (and past inputs in some cases), and its connections are not necessarily unidirectional. The output of a recurrent network is a function of current and past inputs, and its connections are unidirectional. Architecturally, a recurrent network is a feedforward networks with recurrent connections, but it is a feedback network functionally. Since the output of both feedback networks and recurrent networks can be a function of past inputs, and thus they are suitable for sequence processing. Mathematically, the computing of feedforward networks approximates a function mapping, and that of feedback networks approximates finite state machines, pushdown automata, or Turing machines.

Typically, a feedforward network and a recurrent network has a layer of input neurons to receive input, a layer of output neurons to produce output, and often layers of hidden neurons to extend the computing capability of the network. Usually, the neurons of a feedback net-

work are classified into input, hidden, and output neurons functionally but not architecturally. Perceptrons [155] and multi-layer Perceptron [156] are two examples of feedforward networks. Elman network [33] and Jordan network [81] are two examples of recurrent networks. Hopfield networks [75] and BAM [90] two examples of feedback networks.

#### 1.1.4 Implementation of artificial neural networks

Due to the computations required by enormous neural nodes to calculate their thresholded activation and weighted sum on the inputs from their associated input connections in an ANN, ANN systems generally require more intensive computational power but simpler types of computations than current computer systems do. There are many technologies available for implementing ANN, mainly including software simulation which is the most widely used due to the fact that digital computer systems are highly available for writing and testing the simulation programs, electronic hardware (digital VLSI, analog VLSI, hybrid of digital and analog VLSI, etc.) realization which potentially owns both the benefits of high performance and cost-effectiveness currently due to the fact that VLSI provides relatively high performance and is extensively used in current computer systems, optical computing which potentially has the highest performance because it computes at the speed of light, and biological implementation which is biologically closer to biological nervous systems.

#### 1.2 A Brief Review of Artificial Neural Networks

Since the resurgence of research on ANN in 1980s, ANN have attracted much interest of many researchers from various science and engineering disciplines, which is shown by the explosive amount of applications and published technical papers on ANN in 1980s and 1990s. It is beyond the scope of this dissertation to review in detail the rich literature in every research area of ANN. Instead, this section will only briefly review up to late 1980s several representative concepts and landmarks on the common research ground of ANN. Reviewed in much more detail in the related chapters is the literature specific to the research topics covered by this dissertation which explores methods for systematically designing neural architectures for associative memories, database query processing, elementary logical inference, sequence processing,

and syntax analysis. The reference book [189] which provides more than 4000 references is a good source of research material for facilitating a general and in-depth understanding of ANN research.

Two of ANN research problem domains for which few conventional computing solutions exist are

- associative memories which are anticipated to provide the same advantageous capability as human memory does and are currently mainly used in the applications of pattern classification based on their capability for best match and partial match, and

- learning which is anticipated to be used as an efficient and cost-effective alternative to knowledge engineering for automated knowledge acquisition without intensive programming.

Following brief review on ANN literature mainly proceeds along these two intermingled themes which have driven the development of new ANN architectures, models, and algorithms for information processing. The development of formal mathematical models for ANN can be traced back to early 1940s in the work by McCulloch and Pitts [108], which showed that any logical proposition can be represented by a network of interconnected neurons of two states if enough neurons are provided. The computational capability of McCulloch-Pitts neural networks was proved to be equivalent to Turing machines [183] which are the essential model of symbolic computation and can perform any computation that can be described by a finite program in any general purpose language [26].

In 1949, Hebb proposed the first learning rule for neurons [63]. In late 1950s and early 1960s, Rosenblatt introduced a class of neural networks [155], called *perceptrons*, which can learn to classify patterns through *supervised learning*. Rosenblatt's work helped produce a large amount of research activities in this early ANN research era. In 1969, Minsky and Papert showed in their landmark book *Perceptrons* that the computational power of perceptron's single-layer learning algorithm is only able to solve linearly separable problem but not a large class of other problems [118]. With the misinterpretation of such a result, research funding and interest in ANN drastically dropped in the following 1970s. In the dark ages of the 1970s, the

dedicated and everlasting efforts of Amari [7, 8, 9], Anderson [10], Fukushima [39], Grossberg [51, 52, 53], Kohonen [84, 85], and many other researchers ultimately brought in the renascence of ANN in 1980s.

The tremendous resurgence of ANN research interest in 1980s was mainly due to the invention of Hopfield networks [75] which can serve as content-addressable memory or solve combinatorial optimization problems [76], and the introduction of Backpropagation learning algorithm [156] which overcomes the limitation of perceptron's single-layer learning algorithm in linearly separable problems and can be exploited to train multi-layer perceptron to solve nonlinearly separable problems. Since then, Backpropagation multi-layer perceptron has been successfully applied in a variety of applications and has became the most widely used neural network paradigm. The Backpropagation learning algorithm were independently derived by Werbos [193], Parker [138, 139], and LeCun [98], but its popularity was mainly due to the effort of Rumelhart, McClelland, and the PDP Group. Other representative ANN models in the bright 1980s, to name a few, include Hinton, Sejnowski, and Ackley's Boltzmann machine model [1, 67] which can be used to find the global optimum solution for a given problem; Kohonen's Self-Organizing Feature Map [86] which can be trained without supervision to find the organization of relationships among training patterns; Kosko's BAM [89, 90] which can serve as hetero-associative memory and temporal associative memory; Carpenter and Grossberg's ART networks [16, 17, 18] which can be typically used to cluster training patterns via unsupervised training; Radial Basis Function method [114, 146, 147] which was originally used for function interpolation and was also applied to other applications [128, 149]; Hecht-Nielsen's Counterpropagation network [64] which has both supervised as well as unsupervised training stages and can be trained to perform pattern mapping, data compression and associative recall; Fukushima, Miyake, and Ito's Neocognitron [40, 41] which can be trained with supervision to recognize handwritten characters; and recurrent neural networks [33, 81, 144] which allow recursive processing on input string of variable length. A more detailed taxonomy of most neural network architectures and learning algorithms can be found in [56, 102, 112].

#### 1.3 An Overview of the Dissertation

Artificial neural networks, due to their inherent parallelism, potential for fault tolerance, and adaptation through learning, offer an attractive computational paradigm for a variety of applications in computer science and engineering, artificial intelligence, robotics, and cognitive modeling. Despite the success in the application of ANN to a broad range of numeric tasks in pattern classification, control, function approximation, and system identification, the integration of ANN and symbolic computing is only beginning to be explored [22, 23, 47, 70, 72, 73, 99, 145, 172, 179, 185] and is currently viewed as one of important research goals in massively parallel computing and artificial intelligence [65].

Pattern-directed associative processing relies on associative pattern matching and retrieval, is central to many problem solving paradigms in AI (e.g., knowledge based expert systems, case based reasoning) as well as computer science (e.g., database query processing, information retrieval) [54, 97, 181], and dominates the computational requirements of many applications in AI and computer science [55, 97, 127]. This dissertation proposes methods to systematically design massively parallel architectures for pattern-directed symbol processing using neural associative memories as key components. In particular, we propose neural architectures for content-based as well as address-based data storage and recall, database query processing, elementary logical inference, sequence processing, and syntax analysis. Their potential advantages over conventional serial computer implementations of the same functions are examined in the dissertation.

Chapter 2 proposes an approach for the design of a neural memory which supports both content-based (associative) and address-based data storage and retrieval. The proposed neural associative memory allows efficient access of stored data by way of massively parallel best match, partial match and exact match. When used as a content-addressed memory, the proposed neural memory supports recall from partial input patterns, (sequential) multiple recalls, fault-tolerance, precision control and sorted extraction of all stored memory patterns. When used as an address-based memory, the memory module can provide working space for dynamic representations for symbol processing and shared message-passing among neural network mod-

ules within an integrated neural network system. It also provides for real-time update of memory contents by one-shot learning without interference with other stored patterns.

The pattern matching and retrieval process in the proposed neural associative memory which provides massive communication bandwidth and processing units respectively via its massive connections and nodes to match a given pattern with all stored patterns in parallel within one step can be far more efficient (in terms of computation time) than that in a key-based organization of the sort used in conventional computer systems. Chapter 3 takes advantage of this fact to explore the potential benefits of the proposed neural associative memory in the implementation of efficient, noise-tolerant information retrieval and query module in large database systems.

Since most of current digital computer systems store data using address-based memories which are accessed via shared buses, the retrieval of a desired data item satisfying certain criteria (patterns) from a set of candidate data items stored in the memories is inherently sequential and requires certain data organization, which is manipulated and interpreted by a relatively complex program(s), to provide appropriate performance. Although parallel pattern matching can be achieved by current digital computer systems when the systems are provided with multiple processors and memory buses, it would not be cost effective to dedicate such systems to applications which mainly involve intensive pattern matching. The proposed neural associative memory is a cost effective SIMD computer dedicated to pattern association. Therefore, such SIMD capability of the proposed neural associative memory is further explored for relational database queries. The potential merits of ANN's inherent parallelism and noise-tolerance for database query processing are demonstrated by comparing the estimated performance of the proposed neural architecture with that of other techniques commonly used in conventional computer systems for database query processing.

Chapter 4 explores how neural architectures for binary pattern recognition can be extended for elementary logical inference. The proposed neural assemblies for propositional logic are based on geometrical/mathematical analysis. Logical operations such as AND and OR are realized by neural assemblies for the recognition of binary subpatterns. It is known that any proposition

(or equivalently a Boolean function) can be represented in DNF, and hence can be realized by a 2-layer neural architecture assembled using the proposed AND and OR neural assemblies. Since logical AND, logical OR, as well as DNF representation are essential to logical inference and Boolean functions are basic to many applications in science and engineering, we expect the proposed neural assemblies would find use in the construction of modular neural networks for a variety of applications. For instance, Chapter 5 illustrates their use in an neural architecture for sequence processing.

Chapter 5 proposes methods for systematic design of neural architectures for sequence processing, which are used as building blocks to systematically assemble neural architectures for syntax analysis in Chapter 6. Basically, memories and sequence processing mechanisms (with flow control capability) compose current digital computer systems which are driven by sequences of binary codes which are translated from sequences of symbolic program representation that humans can efficiently and effectively read, write, and reason on. Therefore, a computing system integrated from the proposed neural architectures for memories and sequence processing is expected to possess computation capability corresponding to that of current digital computer systems.

Chapter 6 explores the advantages of ANN's inherent parallelism and associative processing capability in the design of modular neural architectures for syntax analysis using a pre-specified grammar — a prototypical symbol processing task. A more general goal of this chapter is to explore the systematical design of massively parallel architectures for symbol processing using the neural associative memory proposed in Chapter 2 and the neural architectures for sequence processing proposed in Chapter 5 as key components.

Since each component in the proposed neural architectures for syntax analysis computes a well-defined symbolic function, it facilitates the systematic synthesis as well as analysis of the resulting symbolic computation at a fairly abstract (symbolic) level. This facilitates rapid design and test of other provably correct prototypes of modular neural architectures for complex symbolic processing using simpler building blocks by way of recursion, composition of elementary symbolic functions, and data representation manipulated by them. The elementary

symbolic functions are represented in terms of binary mappings which are realized provably correctly by basic neural modules using one-shot learning.

Chapter 6 concludes with a summary of the key contributions of this dissertation.

## 2 A NEURAL MEMORY FOR CONTENT AS WELL AS ADDRESS-BASED STORAGE AND RECALL

#### 2.1 Introduction

This chapter presents an approach to design of a neural architecture for both associative (content-addressed) and address-based memories. Several interesting properties of the memories are mathematically analyzed in detail such that it is known that by systematically adjusting the node thresholds and connection weights, the same proposed neural architecture can serve as memories with precision control to perform best match, exact match and partial match which are main knowledge retrieval techniques extensively used in numerous artificial intelligence systems [191]. When used as an associative memory, the proposed neural architecture supports recall from partial input patterns, (sequential) multiple recalls and fault tolerance. When used as an address-based memory, the memory can provide working space for dynamic representations for symbol processing and shared message-passing among neural network modules within an integrated neural network system. It also provides for real-time update of memory contents by one-shot learning without interference with other stored patterns.

It is generally agreed that artificial neural networks (ANN) have demonstrated success in low-level perceptual tasks (e.g., signal processing, pattern recognition) [62, 93, 111, 113]. However, despite their generality (as computational models) and despite the potential advantages of using them as components in general-purpose artificial intelligence systems which usually involve content-based or memory-based knowledge storing and retrieving [47, 70, 72, 73, 99, 173, 179], detailed design and performance tradeoffs in integrated systems of this sort are yet to be fully understood and working prototypes of such systems are only beginning to be developed. Towards this end, an innovative design and careful analysis of neural associative memories with

emphasis on problems and prospects of integrating them into larger systems that combine the advantages of both traditional symbol processing and neural network approaches to artificial intelligence is needed.

A particular class of neural memories built from threshold logic units (Perceptrons or McCulloch-Pitts neurons) is explored from a geometrical/mathematical perspective in this chapter. This analysis provides mathematical foundations for understanding several interesting properties of such memories including: auto as well as hetero-associative recall from partially specified patterns, (sequential) sorted recall of multiple stored patterns with different degrees of match with an input pattern, incremental learning, fault tolerance, and address-based storage and recall (mimicking the behavior of memories used in conventional digital computers). The mathematical analysis also suggests efficient hardware realizations of such memories. This chapter is organized as follows:

- Section 2.1 reviews associative memory, address-based memory, and key properties of multi-layer Perceptrons which form the basis of the proposed neural memories.

- Section 2.2 develops the theoretical foundations and examines the storage capacity of the

proposed binary/bipolar neural memories through an investigation of the spatial distribution and linear separability of vertices in binary/bipolar hypercubes from a geometric

perspective.

- Section 2.3 explores several interesting properties of the proposed memory modules including: recall from partially specified input patterns, (sequential) multiple recalls, and fault tolerance by examining and extending the physical meanings of the settings of connection weights and neuron thresholds in the proposed neural memories.

- Section 2.4 concludes with a summary of the chapter and a brief discussion of related researches.

#### 2.1.1 Information retrieval and binary mapping

In general, most classification and information retrieval problems using discrete input/output values can be viewed in terms of a binary random mapping  $f_I$ , where  $f_I$  is rigidly defined from

a set U of k distinct binary input vectors  $u_1, ..., u_k$  of dimension n to a set V of k binary output vectors  $v_1, ..., v_k$  of dimension m such that  $f_I : U \to V$  and

$$f_I(u_i) = v_i \quad \text{for} \quad 1 \le i \le k \tag{2.1}$$

Note that  $f_I$  is a partial function.

#### 2.1.2 Associative memory (Content-addressed memory)

Since the resurgence of ANN in 1980s, ANN have been applied in many science and engineering disciplines. This is shown by the explosive growth in the number of published technical papers on ANN in 1980s and 1990s. In particular, neural architectures for associative memories have been the subject of considerable research, because of their potential applications in several areas of artificial intelligence, computer science, and cognitive modelling.

The term associative memory (AM) or content-addressed memory refers to a memory system where recall of a stored pattern is accomplished by providing a noisy or partially specified input pattern. Examples of such memory models include Hopfield networks [75], correlation matrix memories [84], bidirectional associative memories [90], among others [9, 59, 91, 125]. A precise definition of binary/bipolar associative memories follows:

Let  $D_H(u, u')$  denote the Hamming distance between binary (bipolar) vectors u and u'. Hamming distance is the number of bits that differ between two binary (bipolar) vectors. Suppose we are given a set U of k binary input vectors  $u_1, ..., u_k$  of dimension n and a set V of k desired binary output vectors  $v_1, ..., v_k$  of dimension m. Then the task is to design an associative memory that can store each of the input-output pattern pairs.

In many applications, it is useful to be able to control the degree of mismatch that is tolerated during information retrieval. This is accomplished by introducing the concept of precision control in associative memory as follows: Define  $U_i^n(p_i) = \{u | u \in \mathbf{B}^n \& D_H(u, u_i) \le p_i\}$ ,  $1 \le i \le k$ , i.e.,  $U_i^n(p_i)$  is the set of n-dimensional binary vectors which have Hamming distance less than or equal to  $p_i$  away from the given n-dimensional binary vector  $u_i$ , where  $\mathbf{B}^n$  is the universe of n-dimensional binary vectors, and  $p_i$  is called allowable precision level and is an adjustable integer parameter.

Information retrieval in a binary associative memory can be specified in terms of a binary associative mapping  $f_A: U^n \to V$  as follows:

$$f_A(x) = v_i \text{ if } x \in U_i^n(p_i), \ 1 \le i \le k$$

(2.2)

where  $U^n = \bigcup_{i=1}^k U_i^n(p_i) = U_1^n(p_1) \cup U_2^n(p_2) \dots \cup U_k^n(p_n)$  and conventionally  $U_i^n(p_i) \cap U_j^n(p_j) = \emptyset$  for  $i \neq j, 1 \leq i, j \leq k$ . For example, if such a memory is used to store and recall uppercase English characters, then U = V and  $u_i = v_i, 1 \leq i \leq 26$ . Suppose the allowable precision levels (i.e., all of the  $p_i$ s) are set equal to (Hamming distance) 4. Then in Figure 2.1, the noisy input patterns 1 and 2 would result in the recall of the stored memory pattern  $\mathbf{T}$ . Multiple recalls are possible in the proposed neural memory when  $\exists i \neq j$  such that  $U_i^n(p_i) \cap U_j^n(p_j) \neq \emptyset$  in which case  $f_A$  is a one-to-many mapping. Most conventional associative memory models seldom tackle the problem of multiple recalls.

Note that  $f_I \subseteq f_A$  if functions  $f_I$  (expression 2.1) and  $f_A$  are viewed as sets of input-output ordered pairs of the functions  $f_I$  and  $f_A$  respectively. That is,

$$f_I \equiv \{(x, f_I(x)) | x \in U\}$$

$$f_A \equiv \{(x, f_A(x)) | x \in U^n\}$$

The partial function  $f_A$  may be extended to a full function  $\hat{f}_A : \mathbf{B}^n \to (V \cup \{<0^m>\})$  for binary associative (information retrieval) memory as follows:

$$\hat{f}_A(x) = \begin{cases} f_A(x) & \text{if } x \in U^n \\ <0^m > & \text{if } x \in (\mathbf{B}^n - U^n) \end{cases}$$

(2.3)

where  $<0^m>$  is the *m*-dimensional binary vector of all zeros and denotes a value which is undefined.

Content-addressed memories can be divided into two categories: auto-associative memories (used primarily for reconstructing a pattern from a noisy or partially specified pattern) and hetero-associative memories which can be used to store associated pattern pairs so that when an input pattern is provided, the associated pattern is retrieved. The types of pattern associations that can be stored in neural associative memories depend on various factors such as: the choice of neural network architecture, the choice of activation functions computed by the neurons,

Figure 2.1 Examples of memory pattern, noisy patterns, and partial pattern

and the algorithm used to set up the parameters (thresholds and weights) associated with the neurons and connections. Thus, a linear associative memory with n input neurons can store and recall perfectly at most n pattern associations. Similar storage capacity results are known for several content-addressed memory models such as the Hopfield network [75, 109], bi-directional associative memories [90], correlation matrix memories [84], etc. A variety of associative memory models are discussed in [62, 93]. As already pointed out, many simple content-addressed memory models studied in the literature are incapable of stable storage and recall of associations between arbitrary pairs of patterns (except under certain restricted circumstances). In such models, whether a pattern can be associated with another critically depends on how the two patterns are coded as bit vectors as well as on all the other pattern associations that have already been stored in memory. The ability to reliably store and recall associations between arbitrary patterns is regarded by many to be a prerequisite for higher level cognitive activity (e.g., logical inference) [35]. The associative memory model proposed in this chapter is designed to reliably store and recall associations between arbitrary pairs of patterns.

#### 2.1.3 Address-based memory

Address-based memory is extensively used for storing both data as well as programs in current computer systems. In cognitive models and artificial intelligence programs based on *Von Neumann* model of computation, i.e., models within the so-called symbolic paradigm [126], address-based memory often serves as the working memory (or scratch-pad) for storing intermediate results during the execution of a program. On the surface, storage and recall of patterns using addresses appear to be very different in spirit from the recall of patterns based on their content (as judged by its similarity to a stored pattern). Indeed, many authors have suggested this to be a primary difference between neural networks (or connectionist models) and traditional artificial intelligence systems. However, this perceived difference is rather superficial given the demonstrable Turing-equivalence of sufficiently powerful neural network models [69, 70]. Therefore, it is rather straightforward to design neural memories capable of address-based storage and recall of patterns as the following discussion illustrates.

A mathematical model for information retrieval in address-based memory can be formulated in terms of a binary random mapping  $f_I$  (expression 2.1) by extending the partial function  $f_I$  to a full function  $\hat{f}_I: \mathbf{B}^n \to (V \cup \{<0^m>\})$  for address-based (information retrieval) memory as follows:

$$\hat{f}_I(x) = \begin{cases} f_I(x) & \text{if } x \in U \\ <0^m > & \text{if } x \in (\mathbf{B}^n - U) \end{cases}$$

(2.4)

$\hat{f}_I$  maps from the set of *n*-bit binary addresses to the set of *m*-bit binary values. The retrieved value (or content of a memory address) is undefined if no pattern has been stored at the corresponding address.

It is well known (in the literature on the design of memory systems for digital computers) that this approach to address-based memory design is not necessarily the most efficient for large address spaces. In this case, hierarchical memory organization using multiple levels of address decoding and multiple memory modules of the type specified above is a more practical alternative [171].

#### 2.1.4 Perceptrons

A 1-layer Perceptron has n input neurons, m output neurons and one layer of connection weights. The output  $y_i$  of output neuron i is given by  $y_i = f_H(\sum_{j=1}^n w_{ij}x_j - \theta_i)$ .  $w_{ij}$  denotes the weight on the link from input neuron j to output neuron i,  $\theta_i$  is the threshold of output neuron i,  $x_j$  is input value at input neuron j, and  $f_H$  is binary hardlimiter function, where

$$f_H(x) = \begin{cases} 1 & \text{if } x \ge 0\\ 0 & \text{otherwise} \end{cases}$$

(2.5)

It is well known that such a 1-layer Perceptron can implement only linearly separable functions from  $\mathbf{R}^n$  to  $\{0,1\}^m$  [118]. We can see the connection weight vector  $w_i = \langle w_{i1}, ..., w_{in} \rangle^T$  and the node threshold  $\theta_i$  as defining a linear hyperplane  $H_i$  which partitions the *n*-dimensional pattern space into two half-spaces, where  $[\cdot]^T$  denotes the *transpose* of a vector or a matrix.

A 2-layer Perceptron has one layer of k hidden neurons (and hence two layers of connection weights with each hidden neuron being connected to every input neuron as well as every output neuron). In this chapter, we use 2-layer Perceptron in which each hidden neuron uses binary hardlimiter function  $f_H$  as activation function. The output of output neuron i is given by  $y_i = f(\sum_{l=1}^k w_{il}z_l - 1)$ ; where  $z_l$  is the output of hidden neuron l, f is binary hardlimiter function  $f_H$  in the model using binary output, and f is bipolar hardlimiter function  $\check{f}_H$  in the model using bipolar output. (The thresholds of all output neurons are set to 1). The bipolar hardlimiter function  $\check{f}_H$  is defined as

$$\check{f}_H(x) = \begin{cases}

1 & \text{if } x \ge 0 \\

-1 & \text{otherwise}

\end{cases}$$

(2.6)

#### 2.2 Multi-layer Perceptrons as Neural Memories

This section describes the synthesis of a binary address-based memory or a binary associative memory using a 2-layer Perceptron. The binary address-based memory has a storage capacity of  $N=2^n$  while the binary associative memory has a storage capacity  $N=\lfloor 2^n/\sum_{i=0}^p C(n,i)\rfloor$ , where n is the number of input neurons and p is the adjustable precision

level (allowable noise level) measured in terms of Hamming distance. A hidden neuron is used for each stored associative pair of input and output patterns. The numbers of input and output neurons are fixed in these models. In the case of associative memory, this amounts to fixing the dimensionality of input and output patterns; while in the address based memory, it is tantamount to fixing the maximum size of the address space and the dimensionality of the patterns stored in memory.

## 2.2.1 The application of linear separability of binary vertices in pattern classification

Note that every *n*-dimensional binary vector is a binary vertex of an *n*-dimensional hypercube. Hereafter, we will use the terms binary vertex and binary vector interchangeably. The following theorem and its proof facilitate the systematic synthesis of the proposed neural memories.

**Theorem 2.1**: Let u be a binary vector of dimension n, i.e.,  $u = \langle u_1, ..., u_n \rangle^T$  where  $u_i \in \{0,1\}$  for  $1 \leq i \leq n$ . Let  $\overline{u} = \langle \overline{u}_1, ..., \overline{u}_n \rangle^T$  be the complement of the binary vector u. That is,  $u_i + \overline{u}_i = 1$  for  $1 \leq i \leq n$ . Let  $u - \overline{u} = u^{ref_u} = \langle u_1^{ref_u}, ..., u_n^{ref_u} \rangle^T$ . Note that  $u_i^{ref_u} \in \{1, -1\}$  for  $1 \leq i \leq n$ . Let us call  $u^{ref_u}$  the reference vector. Let  $S_p^u$  be the set of n-dimensional binary vertices which are at a Hamming distance p away from vertex  $u, 0 \leq p \leq n$ . Then every binary vertex  $x \in S_p^u$  falls on an n-dimensional linear hyperplane  $H_p^{n,u}$  which is perpendicular to the reference vector  $u^{ref_u}$ . Furthermore, if  $H^{n,u} = \{H_p^{n,u}; 0 \leq p \leq n\}$ , the n-dimensional linear hyperplanes in  $H^{n,u}$  are mutually parallel.

**Proof:** Let x be a binary vertex in  $S_p^u$ ,  $x-\overline{u}=x^{ref_u}=< x_1^{ref_u}, ..., x_n^{ref_u}>^T$  and  $l_x^u$  be the length of the projection of  $x^{ref_u}$  onto the reference vector  $u^{ref_u}$ . Note that  $x_i^{ref_u}=0$  or 1 if  $u_i^{ref_u}=1$ , and  $x_i^{ref_u}=0$  or -1 if  $u_i^{ref_u}=-1$  for  $1\leq i\leq n$ . Note also that there are p components  $x_i^{ref_u}$  of  $x^{ref_u}$  such that  $x_i^{ref_u}=0$  and (n-p) components  $x_j^{ref_u}$  of  $x^{ref_u}$  such that  $x_i^{ref_u}=1$  or -1, where  $1\leq i,j\leq n$ . Let  $\|\cdot\|$  denote the length of a vector. Then

$$l_x^u = \frac{1}{\|u^{ref_u}\|} (u^{ref_u})^T x^{ref_u}$$

(2.7)

$$= \frac{1}{\|u^{ref_u}\|} \sum_{i=1}^n u_i^{ref_u} x_i^{ref_u} \tag{2.8}$$

$$= \frac{1}{\|u^{ref_u}\|} \left( \sum_{x_i^{ref_u} = 1 \text{ or } -1}^{n-p} u_j^{ref_u} x_j^{ref_u} + \sum_{x_i^{ref_u} = 0}^{p} u_i^{ref_u} x_i^{ref_u} \right)$$

(2.9)

$$= \frac{1}{\|u^{ref_u}\|}(n-p) \tag{2.10}$$

$$= \frac{1}{\sqrt{n}}(n-p) \tag{2.11}$$

The expression defining the n-dimensional linear hyperplane  $H_p^{n,u}, \ 0 \le p \le n$ , is

$$H_p^{n,u} \equiv \left(\sum_{i=1}^n (2u_i - 1)x_i\right) - \left(\sum_{i=1}^n u_i - p\right) = 0$$

(2.12)

which can be derived as follows. Let x be a binary vertex on hyperplane  $H_p^{n,u}$ , where  $0 \le p \le n$ . From expressions 2.7 and 2.11, we have:

$$l_x^u = \frac{1}{\|u^{ref_u}\|} (u^{ref_u})^T x^{ref_u} = \frac{1}{\sqrt{n}} (u - \overline{u})^T (x - \overline{u}) = \frac{1}{\sqrt{n}} (n - p)$$

(2.13)

Thus,

$$(u - \overline{u})^{T}(x - \overline{u}) = (n - p)$$

(2.14)

So the defining expression of the hyperplane  $H_p^{n,u},\, 0\leq p\leq n,$  is given by:

$$H_p^{n,u} \equiv (u - \overline{u})^T (x - \overline{u}) = (n - p)$$

(2.15)

$$\equiv (u - \overline{u})^T x - (u - \overline{u})^T \overline{u} - (n - p) = 0, \quad note \quad u^T \overline{u} = 0$$

(2.16)

$$\equiv (u - \overline{u})^T x - (n - ||\overline{u}||^2 - p) = 0, \quad note \quad ||u||^2 + ||\overline{u}||^2 = n$$

(2.17)

$$\equiv (u - \overline{u})^T x - (||u||^2 - p) = 0$$

(2.18)

Figure 2.2 The spatial distribution of a 3-dimensional and an n-dimensional binary hypercubes

$$\equiv (u_1 - \overline{u}_1)x_1 + \dots + (u_n - \overline{u}_n)x_n - (\|u\|^2 - p) = 0$$

(2.19)

$$\equiv (2u_1 - 1)x_1 + \dots + (2u_n - 1)x_n - (\|u\|^2 - p) = 0$$

(2.20)

$$\equiv \left(\sum_{i=1}^{n} (2u_i - 1)x_i\right) - (\|u\|^2 - p) = 0 \tag{2.21}$$

$$\equiv \left(\sum_{i=1}^{n} (2u_i - 1)x_i\right) - \left(\sum_{i=1}^{n} u_i - p\right) = 0 \tag{2.22}$$

Note that  $||u||^2 = \sum_{i=1}^n u_i$  since u is a binary vector. From above, it is known that the expressions defining the n+1 n-dimensional mutually parallel linear hyperplanes  $H_p^{n,u}$ 's,  $0 \le p \le n$ , have same coefficients but different constant terms. Every hyperplane  $H_p^{n,u}$ , where  $0 \le p \le n$ , can serve as a linear separating hyperplane to partition all n-dimensional binary vertices into two sets. Such a linear separating hyperplane can be efficiently implemented for 2-class pattern classification by a 1-layer Perceptron with one output neuron. The output neuron has a threshold of  $\sum_{i=1}^n u_i - p$  and the connection weight on the link from input neuron i is given by  $2u_i - 1 (= u_i - \overline{u}_i)$  for  $1 \le i \le n$ , where n is the number of input neurons.

When the separating hyperplane  $H_p^{n,u}$  is realized by a 1-layer, 1-output Perceptron, the value of  $2u_i - 1$  is either 1 or -1,  $x_i$  is either 1 or 0, and  $(2u_i - 1)x_i$  can therefore be 1, 0 or -1; and  $\sum_{i=1}^n u_i$  is integer. Also note that the maximum activation of the 1-layer Perceptron

is p and minimum value is -(n-p); since the separating hyperplane  $H_p^{n,u}$  is defined as  $(u-\overline{u})(x-\overline{u})^T-(n-p)=0$ , the maximum value of  $(u-\overline{u})(x-\overline{u})^T$  is n when x=u, and the minimum value of  $(u-\overline{u})(x-\overline{u})^T$  is 0 when  $x=\overline{u}$ .

#### 2.2.2 Best match: pattern classification with precision control

Since each binary vertex of dimension n on hyperplane  $H_p^{n,u}$  is Hamming distance p away from vertex u, there are  $N_p = C(n,p) = \frac{n!}{(n-p)!p!}$  such binary vertices of dimension n on hyperplane  $H_p^{n,u}$ , where  $0 \le p \le n$ . The separating hyperplane  $H_p^{n,u}$  partitions all the binary vertices of a binary n-hypercube into two sets. One set contains  $N_A = \sum_{i=0}^p N_i = \sum_{i=0}^p C(n,i)$  binary vertices that are at a Hamming distance less than or equal to p away from vertex u, and the other contains  $N_B = \sum_{i=p+1}^n N_i = \sum_{i=p+1}^n C(n,i)$  binary vertices that are at a Hamming distance more than p away from vertex u. Let us call the former partition the associative partition (denoted by  $\alpha_p^u$ ) of u, the vertex u the center of that associative partition, and p the radius of the associative partition. Note that both  $H_p^{n,u}$  and  $\alpha_p^u$  are defined by the given binary exemplar pattern u and its precision level p.

In theory, an n-hypercube can be almost equally partitioned by  $N = \lfloor 2^n / \sum_{i=0}^p C(n,i) \rfloor$  such associative partitions as  $\alpha_p^u$  with each associative partition containing  $\sum_{i=0}^p C(n,i)$  n-dimensional binary vertices which are all at a Hamming distance less than or equal to p away from their corresponding partition center. The partition centers correspond to the given binary exemplar patterns.

We say that an associative partition  $\alpha_{p_i}^{\nu_i}$  is not isolated from another associative partition  $\alpha_{p_j}^{\nu_j}$   $(i \neq j)$  if  $\alpha_{p_i}^{\nu_i} \cap \alpha_{p_j}^{\nu_j} \neq \emptyset$ . Thus, if two associative partitions are not isolated from each other, they overlap and as a result, there is at least one binary vector that is a member of both partitions. The separating hyperplanes (or equivalently, associative partitions) can be implemented in a 1-layer Perceptron with N output neurons to recognize N patterns with precision level (allowable noise level) up to Hamming distance  $p_i$  for exemplar pattern  $\nu_i$ ,  $1 \leq i \leq N$ , provided the precision levels  $(p_i$ s) are chosen to ensure that each associative partition is isolated from every other. When  $x \in \alpha_{p_i}^{\nu_i}$  is fed into the 1-layer Perceptron, the

output neuron that corresponds to the separating hyperplane  $H_{p_i}^{n,\nu_i}$  is activated to produce an output of 1. In order to ensure that the associative partitions corresponding to two exemplar patterns  $\nu_i$  and  $\nu_j$  are isolated from each other,  $D_H(\nu_i,\nu_j)$  has to be greater than  $(p_i+p_j)$  where  $p_i$  and  $p_j$  are the allowable precision levels. Otherwise, the associative partitions of  $\nu_i$  and  $\nu_j$  would overlap with each other, and when an input pattern x, where  $D_H(x,\nu_i) \leq p_i$  and  $D_H(x,\nu_j) \leq p_j$ , is fed into the 1-layer Perceptron, the output neurons for the two exemplar patterns  $\nu_i$  and  $\nu_j$  will produce 1 as their outputs. In this case, the input pattern x cannot be unambiguously classified as it falls in the region of overlap between the associative partitions  $\alpha_{p_i}^{\nu_i}$  and  $\alpha_{p_j}^{\nu_j}$ .

#### 2.2.3 Storage capacity

Suppose input patterns are  $10\times10$  arrays of binary pixels (see Figure 2.1). Then 100 input neurons are required to implement such a 1-layer Perceptron for pattern classification. The number of possible input patterns is  $2^{100}\approx10^{30}$ . An output neuron is needed for each distinct exemplar pattern. Table 2.1 shows the corresponding maximal storage capacity of the 1-layer Perceptrons designed for a range of different allowable noise levels. Table 2.1 also suggests that a 1-layer Perceptron with n input neurons has very high storage capacity for classifying binary patterns and that the allowable precision (noise) levels of less than 30% are desirable for reliable classification.

#### 2.2.4 Synthesis of associative and address-based memories

Given a set U of k distinct binary input vectors  $u_1, ..., u_k$  of dimension n, where  $u_i = \langle u_{i1}, ..., u_{in} \rangle^T$  and  $u_{ig} \in \{0, 1\}$  for  $1 \le i \le k \ \& \ 1 \le g \le n$ ; and a set V of k desired binary (bipolar) output vectors  $v_1, ..., v_k$  of dimension m, where  $v_i = \langle v_{i1}, ..., v_{im} \rangle^T$  and  $v_{ih} \in \{0, 1\}$  (or  $\{-1, 1\}$ ) for  $1 \le i \le k \ \& \ 1 \le h \le m$ . Assume the Hamming distance between any two binary vectors in U is at least 2p + 1, where  $p \in \mathbb{N}$ . This ensures that all associative partitions

Table 2.1 The corresponding maximal storage capacity of a 1-layer Perceptron with 100 input neurons for classifying binary patterns for a range of allowable noise levels

| allowable noise | maximal capacity                                                                                 |

|-----------------|--------------------------------------------------------------------------------------------------|

| 0%              | $N = \lfloor 2^{100} / \sum_{i=0}^{100 \times 0} C(100, i) \rfloor \approx 1.0 \times 10^{30}$   |

| 10%             | $N = \lfloor 2^{100} / \sum_{i=0}^{100 \times 0.1} C(100, i) \rfloor \approx 5.0 \times 10^{16}$ |

| 20%             | $N = \lfloor 2^{100} / \sum_{i=0}^{100 \times 0.2} C(100, i) \rfloor \approx 1.4 \times 10^9$    |

| 30%             | $N = \lfloor 2^{100} / \sum_{i=0}^{100 \times 0.3} C(100, i) \rfloor \approx 2.4 \times 10^4$    |

| 40%             | $N = \lfloor 2^{100} / \sum_{i=0}^{100 \times 0.4} C(100, i) \rfloor \approx 38$                 |

| 50%             | N=2                                                                                              |

would be isolated with the precision level being set at p.

We can now design a neural architecture for information retrieval using address-based memory, denoted by function  $\hat{f}_I$  (defined by expression 2.4), or associative memory, denoted by function  $\hat{f}_A$  (defined by expression 2.3). For this purpose, a memory module of a 2-layer Perceptron can be synthesized using the 1-layer Perceptrons, proposed for pattern classification in Section 2.2.1, as follows:

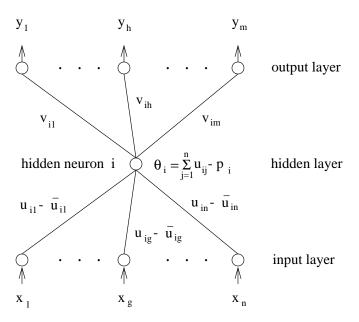

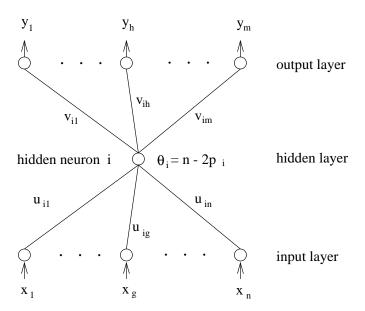

The memory module (using binary input) has n input, k hidden, and m output neurons. For each associative ordered pair  $(u_i, v_i)$ , where  $1 \le i \le k$ , we create a hidden neuron i with threshold  $\sum_{j=1}^n u_{ij} - p_i$  (see Figure 2.3), where  $p_i \in \mathbf{N}$  and  $p_i \le p$  is the adjustable precision level for that associative pair. The connection weight from input neuron g to hidden neuron i is  $2u_{ig}-1$  (=  $u_{ig}-\overline{u}_{ig}$ ) and that from hidden neuron i to output neuron h is  $v_{ih}$ . The threshold for each of the output neurons is set to 1. The activation functions at hidden neurons are binary hardlimiter function  $f_H$ . The activation functions at output neurons are binary hardlimiter function  $f_H$  (expression 2.5) if the desired output of output neurons is binary. The activation functions at output neurons are bipolar hardlimiter function  $f_H$  (expression 2.6) if the desired output of output neurons is binary.

Since input is binary, the weights in the 1st-layer connections of the memory module are either 1 or -1. A bit of an input pattern that is wrongly on (with respect to a stored pattern), contributes -1 to the activation of the corresponding hidden neuron and a bit of an input pattern that is rightly on (with respect to a stored pattern) contributes +1 to the activation

Figure 2.3 The setting of connection weights and hidden node threshold in the proposed neural memory (a 2-layer Perceptron with binary input) for a given associated memory pair

of the corresponding hidden neuron. A bit of an input pattern that is (rightly or wrongly) off (with respect to a stored pattern) contributes 0 to the activation of the corresponding hidden neuron. Each hidden neuron sums up the contributions to its activation from its 1st-layer connections, compares the result with its threshold (which equals the number of 1 in the stored memory pattern minus its desired precision level), and produces output value 1 if its activation exceeds or equals its threshold. If one of the hidden neurons is turned on, one of the stored memory patterns will be recalled by that hidden neuron. Note that an input pattern is matched against all the stored memory patterns in parallel. If the time delay for computing the activation at a neuron is fixed, the time complexity for such a pattern matching process is O(1). Note that this is attained at the cost of a hidden neuron (and its connections) for each stored association.

Since all the associative partitions are isolated from each other, when the memory module is presented with a binary input vector  $x \in \alpha_{p_i}^{u_i}$ , only the hidden neuron *i* produces an output of 1 and the output values from all other hidden neurons are 0. So the value at output neuron

j is  $v_{ij}$ , and hence the output binary vector will be  $\langle v_{i1}, ..., v_{im} \rangle^T = v_i$ . Since for each memory association pair a hidden neuron is created and its creation or deletion is independent of other stored associative pairs, this particular design of associative memory lends itself to rapid one-shot incremental learning with no interference with previously stored associations.

It is also worth pointing out that exactly the same network architecture can be used to realize both associative as well as address-based memory. If  $p_i$  is set as 0,  $|\alpha_{p_i}^{u_i}| = 1$  and the memory module functions as an address-based memory when  $2^n$  hidden neurons are used to resolve all possible addresses; and if  $1 \leq p_i \leq p$ ,  $|\alpha_{p_i}^{u_i}| > 1$  and it can be used as an associative memory with adjustable precision control. (|A| denotes the cardinality of a set A). Address-based memory, extensively used in current computer system, can serve as working space of dynamic representations for symbol processing and shared message-passing space among neural network modules in an integrated neural network system. As working space for symbol manipulation, neural memories have to allow run-time update without learning and do not degrade when the number of stored memory patterns increases. Note that the proposed neural address-based memory has these two properties.

#### 2.2.5 Exact match: binary mapping Perceptron (BMP) module

Let U be a set of k distinct binary input vectors  $u_1, ..., u_k$  of dimension n, where  $u_i = \langle u_{i1}, ..., u_{in} \rangle^T$  and  $u_{ig} \in \{0, 1\}$  for  $1 \le i \le k \& 1 \le g \le n$ ; and V be a set of k desired binary output vectors  $v_1, ..., v_k$  of dimension m, where  $v_i = \langle v_{i1}, ..., v_{im} \rangle^T$  and  $v_{ih} \in \{0, 1\}$  for  $1 \le i \le k \& 1 \le h \le m$ . Consider a binary mapping function  $f_{BMP} : \mathbf{B}^n \to (V \cup \{\langle 0^m \rangle\})$  defined as follows:

$$f_{BMP}(x) = \begin{cases} v_i & \text{if } x = u_i, 1 \le i \le n \\ <0^m > & \text{if } x \in (\mathbf{B}^n - U) \end{cases}$$

(2.23)

where  $\mathbf{B}^n$  is the *n*-dimensional binary space. A BMP module for the binary mapping function  $f_{BMP}$  can be synthesized using a 2-layer Perceptron as follows: The BMP module (see Figure 2.4) has *n* input, *k* hidden and *m* output neurons. For each binary mapping ordered pair  $(u_i, v_i)$ , where  $1 \leq i \leq k$ , we create a hidden neuron *i* with threshold  $\sum_{j=1}^n u_{ij}$ . The connection weight from input neuron *g* to hidden neuron *i* is  $2u_{ig} - 1$  (=  $u_{ig} - \overline{u}_{ig}$ ) and that from hidden

Figure 2.4 The settings of connection weights and hidden node threshold in the proposed BMP module for an associated binary mapping ordered pair

neuron i to output neuron h is  $v_{ih}$ . The threshold for each of the output neurons is set to 1. The activation functions at hidden and output neurons are binary hardlimiter function  $f_H$ .